# Design And Implementation of High-Performance Timing-Error-Tolerant Circuit Using 45nm

Sampathirao Srihari Raju<sup>1</sup>, Smt. Jhansi Rani Kaka<sup>2</sup> <sup>1</sup>M.Tech, VLSI & EMBEDDED SYSTEMS , Department of ECE, UCEK(A), JNTUK, Kakinada, India. <sup>2</sup>Assistant Professor, Department of ECE, UCEK(A), JNTUK, Kakinada, India.

## ABSTRACT

**Article Info** Volume 9, Issue 5 Page Number : 309-314

Publication Issue September-October-2022

Article History Accepted : 01 Oct 2022 Published : 09 Oct 2022 This work uses the clock technique to show timing error and timing error tolerant circuits. Timing faults are recognized, and fixed by adjusting the clock of the flip flop while changing the system clock and using the fewest logics available. To deal with a timing error, numerous techniques have been introduced. Conventional strategies that can minimize a timing issue, on the other end, were indeed concentrated mainly on time-delaying signaling pathways & overly complicated processes, culminating in some kind of a timing difficulty for clock-based devices while also peripheral devices operating costs. In this paper, we report a novel timing-error-tolerant paradigm based on a simple way for asynchronously clarifying a timing issue. To heal a temporal lag, the procedure involves investing time in a clock-based application and changing the clock within a flip-flop. The suggested model, in particular, has considerably decreased memory requirements due to its compact construction, as compared to earlier timing-error-tolerant devices that can truly recover the fault instantly. In order to examine this text, it is also necessary to be familiar with a number of other basic terms, including channel estimate, error systems, softness error, time error tolerant system, and timing error.

Keywords : Error tolerant, bit-interleaving, clock gating, error correction and detection, time borrowing.

# I. INTRODUCTION

Timing mistakes are a development is necessary of operational challenges in Nano scale technology, high complexity, and inter frequency ICs. A new localized error detection and correction technique based on bit flipping flip-flops has been proposed in this study. When a timing issue is discovered, the accompanying flip-output flop's is supplied to remedy the problem. Like the clock frequency rises, the quantity of timing errors rises with it. Technical requirements in the design are often more vulnerable to timing errors when the clock period is decreased. Differences in the CMOS process, power supply, and temperature also affect the performance of current IC's resulting in a high rate of timing errors. The latency of the circuit can differ significantly from the normal scenario once the supply voltage falls. The worst case of process,

**Copyright: O** the author(s), publisher and licensee Technoscience Academy. This is an open-access article distributed under the terms of the Creative Commons Attribution Non-Commercial License, which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited

voltage, and temperature conditions. One of the major difficulties confronting the semiconductor industry right now is process variability in device and circuit parameters.

Dynamic parameter differences can occur during chip functioning as a response to environmental and work changes, as opposed to static parameter changes that can occur during chip manufacturing. Active variations include supply voltage hang-ups, temperature swings, and transistor fading deterioration. Variations change the timing and power cost advantages of the circuit, and if not managed effectively, they can adversely affect performance of the system, energy, and overall reliability [2].

Even though increasing safety factors helps to handle fluctuations, also it results in substantial loss in performance or power consumption. Adapting strategies that adjust for variances have already been explored as a result. Critical path replication devices having durations that are highly associated with the critical path delays of the actual logic block are an appealing solution. Tolerate timing variation while operating at decreased safety margins, apply in-situ errors identification and repair systems in timingcritical paths. When the chance of critical-path activation is large, however, the performance in terms of energy overheads of error correction can be significant.

Connecting wire helps to fan-out delay by expanding the number of output connections. Ability to control parameters in a si fabricator technician, influencing battery topography and transistor measurements by a Mobile phone library developer and a Programmable logic chip designer, controlling synthesis, place & route, and cell selection with CAD tools, and controlling RTL and Layout generator by a designer can all be used to control the delay. Provisions for setting input arrival timings (related to the clock) and output parameters will be included in tools that are expected to do something about the timing behaviors (such as synthesisers) (set-up times of next stage). For outputs, setup time is deduced by what it connections to, whereas clk-to-q for circuit inputs is determined by where it originated. The delay caused by the first latch causes setup time, while the disruption caused by the second latching causes setup time. Clock A delay caused by the second latch in Flip flops leads to a Q delay.

This research presents a strategy for anticipating timing mistakes in a pipelined program to enhance endurance to logic phase lag time variations when performing at a clock cycle smaller than that of the critical path propagation delay having lower service effect (just over a clock cycle). This strategy is to reduce timing issues, this integrates the sense of time borrow with cutting-edge circuitry. Times borrow is a well-known notion in pipelines with pulsed latching or soft-edge flip-flops, in which legal signal transitions are allowed even beyond the clock edge (within the limited transparent time period), resulting in accurate values propagating to the next stage. Pipelines with lowest power-delay combination could be required to optimize the transparent windows of pulsed latches.

#### **II. EARLIER WORK**

The development of a new timing-error-tolerant technology that can correct a timing issue is underway. When a timing problem creates a delay in the arrival of an input on a flip-flop, the recommended method can detect it and the flip-flop passes through the data by making a translucent window.

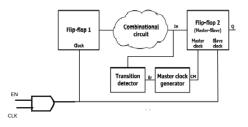

## Timing error tolerant circuit:

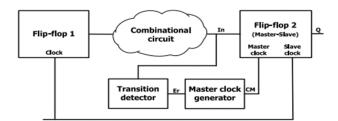

Fig.1: Block diagram of timing error tolerant circuit A transition detectors and just a master clock generator are included in present scheme, as shown in Fig. The transition detectors recognises a flip-input flop's transition & generates an error-flagged signal pulse. The master clock generator generates a pulse for a predefined timeframe once the clock is high, based on the output of the transition detector. The flip-flop passes the input to the output whereas a pulse is 1, since the pulse controls a master clock in the flip-flop, which creates a transparent window. As a result, the flip-abnormal flop's data can be restored using delayed normal data. To avoid a hold time violation, a pulse is created with the shortest time possible.

Fig. 2 (a)

Master clock generator

Fig.2 (b)

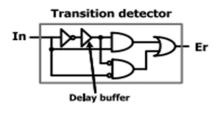

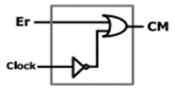

Fig. 2 Internal circuits of (a): transition detector (b): master clock generator

A Transition detector's internal circuit is illustrated above. The transition detector consists of an inverter to which the buffer is linked, and also the buffer's output is sent to one of the inputs for the AND ass well as Bubbled AND gates, while the gates' inputs are obtained from the input. The OR gates, which emit the error signal, are coupled to the output of these gates. When the shift from low to high and high to zero occurs, the error occurred. The master clock generator of the master latch takes this erroneous signal as an input. That's the master clock generator's internal design. It is made up of an OR gate having error & clock signal inputs that are coupled via an inverter. It generates a signal known as CM, which is used as the Master Latch's clock input.

Result in delayed input data, whenever a timing fault appears on the flip-flop 2's data input, the flip-flop 2 stores irregular data to the output Q. A changeover detectors, which would be situated between a combinational circuit and the flip-flop 2, emits an error pulse after the delay normal data have arrived on the input of flip-flop 2. By detecting both a rising and falling edge in the data, the transitional detector can identify simultaneously up - and - down edges the delayed normal input. the AND gate as well as an inverter Moreover, through adding a delay buffer into to the transitional detectors, the transition detector provides a custom period of a pulses, allowing the transparent window to be maintained for a good length of time. Based on the error pulses as well as clock, the master clock generator generates a clock for the master (CM).

After a timing error, a CM is elevated for just a short time due to the OR gate as well as inverter with in master clock generator. The flip-flop 2 becomes transparent whenever the CM is high, and t is saved by flip-flop 2. As a result, the normal input is used to fix the erroneous output Q. The suggested system detects and corrects the timing mistake while the clock is high, because the timing problem usually occurs after a rising edge of the clock. Whenever the combinational circuit's latency exceeds the half-time of the clock period, the suggested methodology is used in essential pathways. Because the master latch is transparent during the pulse time, all postponed incoming data signal is retrieved in the case of a single-stage fault. However, because the second flip-

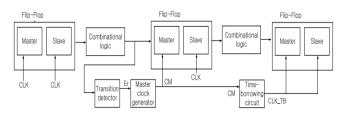

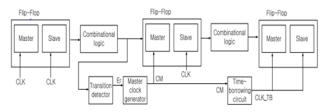

flop lacks setup time, a sequential error occurs, and the late arriving data signal in the second phase cannot be stored due to the setup-time violation. To deal with the successive-stage error, the timeborrowing approach was developed. A period circuit is included in the next phase, as shown.

Fig.3 Block diagram of proposed timing error

Fig.4: Internal circuit of Time borrow circuit. Whenever a timing error in first stage's input data occurs, the CM signal is set to 1, causing the CM SR high level to be induced. Q is set to 1 once CLK has fallen IN the second step, the delayed CLK (CLKDD) is selected as the primary CLK, with the Q signal determining the high period. After all, the new CLK maintains a transparent window open for a long enough amount of time. After a timing issue, the CM remains high for a given amount of time. As a result, the postponed information can be stored in the same way that regular data is. Any place could be used with the time-borrowing system. The flip-flop just takes a few seconds to set up.

#### **III. PROPOSED WORK**

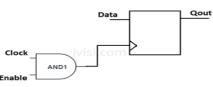

Inside this article, researchers use the clock gating technique to demonstrate a timing error tolerant circuit and a timing error with time borrowing circuit. Clock gating is a low-power approach that can help you save even more energy. Clock gating is implemented using a logical AND gate with two inputs: one is for clock and one for enable. Enable Pin can be used to provide controlling action to the circuit.

VLSI chips are still evolving, with engineers seeking for ways to improve IC performance, such as reducing area and power consumption. Fault current, which can be caused by gate generated drain leakage current, sub - threshold leakage, the hot electron effect, gate tunneling, and other factors, is one of the most critical problems that designers face.

Dynamic power, short circuit power, and static power could all be added together just to calculate CMOS' total power usage. The amount of power dissipated by a chip per unit area is referred to as power density. Static and dynamic are the two categories. When switching activity occurs in the inputs and outputs of a chip, each CMOS device dissipates power. When compared to transistors that switch slowly, transistors that switch quickly dissipate more energy. The clock signal employed in the circuit is the primary cause of dynamic power dissipation.

Low-power approaches such as power gating and clocks gating are used to limit leaky energy dissipation. The above are the principles of energy gating and clock gating: Various solutions have indeed been devised to reduce the clock switching activities. One of them is clock-gating. It is based on the idea of turning off the clock to flip-flops or memory sections that aren't in use at the time, hence avoiding unnecessary shifting and conserving dynamic power.

The leakage currents in the MOSFET device are primarily responsible for the static power consumption. It occurs when an undesirable current (sub threshold current) flows through a transistor's channel even when the transistor is turned off. The threshold voltage of the transistors in the circuits is considerably influenced as a result of this.

Fig.5: Block diagram of Clock gating

The timing error tolerant circuit that uses clock gating is depicted in the diagram below.

Fig.6: Timing error tolerant circuit using clock gating Nevertheless, when a consecutive error occurs so because 2nd stage flip-flop lack setup time, the delayed arriving data signal in the second stage cannot be stored due to the setup-time violation. To combat with the successive-stage miscalculation, the timeborrowing approach was devised. A time-borrowing circuit is depicted in the second stage.

Fig.7: Block diagram of proposed timing error using clock gating.

# IV. EXPERIMENTAL RESULTS

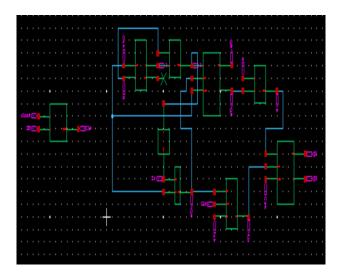

The Tanner EDA Tool was used to simulate utilising 45nm CMOS technology. The same fan-in and fanout were used in all simulations.

For the suggested schematic of block diagram using clock gating.

Fig8: schematic of proposed circuit. Whereas Figure 9 shows the suggested clock gating circuit, a transient analysis was performed.

Fig9: Transient results of proposed circuit.

Comparison between existing and proposed methods of Timing error tolerant circuit.

|          | Area | Power   | Delay   |

|----------|------|---------|---------|

| Existing | 216  | 3.841mW | 72.09ns |

| Proposed | 222  | 1.343mW | 41.8ns  |

Table 1: comparison between conventional and proposed methods.

From the results observed from the table-1, we can conclude that the proposed circuit is better in terms of

power and delay by employing clock gating method in the tolerant circuit.

### V. CONCLUSION

In this work, we offer a timing-error-tolerant approach that uses clock gating to instantly repair a timing fault in a compact circuit topology. Using the Timing error tolerant circuit and Tolerant circuit with Time borrowed methodology, we had presented an effective technique for identifying and correcting timing faults. The improper data transition that after clock's edge can be recognized and repaired in the critical route by managing the clock's transparent window. A small number of logics are used to effectively rectify the timing error.

## VI. REFERENCES

- J. W. McPherson, Reliability challenges for 45 nm and beyond, in Proc. 43rd ACM/IEEE Design Automat. Conf., Jul. 2006, pp. 176–181.

- [2]. S. Mitra, N. Seifert, M. Zhang, Q. Shi, and K. S. Kim, Robust system design with built-in softerror resilience, Computer, vol. 38, no. 2, pp. 43–52, Feb. 2005.

- [3]. S. P. Park, K. Roy, and K. Kang, Reliability implications of bias temperature instability in digital ICs, IEEE Des. Test Comput., vol. 23, no. 6, pp. 8–17, Nov./Dec. 2009.

- [4]. M. Seok, G. Chen, S. Hanson, M. Wieckowski,

D. Blaauw, and D. Sylvester, CAS-FEST 2010: Mitigating variability in near-threshold computing, IEEE J. Emerg. Sel. Topics Circuits Syst., vol. 1, no. 1, pp. 42–49, Mar. 2011.

- [5]. M. Agarwal, B. C. Paul, M. Zhang, and S. Mitra, Circuit failure prediction and its application to transistor aging, in Proc. 25th IEEE VLSI Test Symmposium (VTS), May 2007, pp. 277–284.

- [6]. M. Agarwal et al., Optimized circuit failure prediction for aging: Practicality and promise,

in Proc. IEEE Int. Test Conf., Oct. 2008, pp. 1–10.

- [7]. M. Nicolaidis, Time redundancy based softerror tolerance to rescue nanometer technologies, in Proc. 17th IEEE VLSI Test Symp., Apr. 1999, pp. 86–94.

- [8]. L. Anghel and M. Nicolaidis, Cost reduction and evaluation of a temporary faults detecting technique, in Proc. Design, Automat. Test Eur. Conf. Exhib., Mar. 2000, pp. 591–598.

- [9]. S. Valadimas, A. Floros, Y. Tsiatouhas, A. Arapoyanni, and X. Kavousianos, The time dilation technique for timing error tolerance, IEEE Trans. Comput., vol. 63, no. 5, pp. 1277– 1286, May 2014.

## Cite this article as :

Sampathirao Srihari Raju, Smt. Jhansi Rani Kaka, "Design And Implementation of High-Performance Timing-Error-Tolerant Circuit Using 45nm", International Journal of Scientific Research in Science and Technology (IJSRST), Online ISSN : 2395-602X, Print ISSN : 2395-6011, Volume 9 Issue 5, pp. 309-314, September-October 2022.

Journal URL : https://ijsrst.com/IJSRST1229559