Themed Section: Science and Technology

DOI: 10.32628/IJSRST

# **Study of OP-AMP Using Compensation Design**

#### Lav Kumar

M. Phil. Students, Department of Physics, B. R. A. Bihar University, Muzaffarpur-842001, Bihar, India

#### ABSTRACT

In this paper, we report on study of design of operational amplifier using compensation techniques. Operational Amplifiers (Op-amps) are one of the most widely used building blocks for analog and mixed-signal systems. They are employed from dc bias applications to high-speed amplifiers and filters. General purpose op-amps can be used as buffers, summers, integrators, differentiators, comparators, negative impedance converters, and many other applications. With the quick improvements of computer aided design (CAD) tools, advancements of semiconductor modeling, steady miniaturization of transistor scaling, and the progress of fabrication processes, the integrated circuit market is growing rapidly.

**Keywords:** Op-amps, CAD, Compensation Techniques, CMOS.

## I. INTRODUCTION

Nowadays, complementary metal-oxide semiconductor (CMOS) technology has become dominant over bipolar technology for analog circuit design in a mixed-signal system due to the industry trend of applying standard process technologies to implement both analog circuits and digital circuits on the same chip. While many digital circuits can be adapted to a smaller device level with a smaller power supply, most existing analog circuitry requires considerable change or even a redesign to accomplish the same feat. With transistor length being scaled down to a few tens of nanometers, analog circuits are becoming increasingly more difficult to improve upon.

The classic Widlar op-amp architecture, originally developed for bipolar devices, has required modification for use with CMOS devices. In particular, it has proved difficult to match the open loop gain of bipolar op-amps with CMOS technology [3, 4]. This is due to the inherently lower transconductance of CMOS devices as well as the gain reduction due to short channel effects that come into play for submicron CMOS processes. As a result, gain boosting schemes have been reported [5, 6]to improve the gain. These gain enhancing methods often require more complicated circuit structures and higher power supply voltage, and may produce a limited output voltage swing. Multiple stage amplifiers may be used for higher gain analog circuit designs. Nevertheless, multistage amplifiers generally are difficult to compensate.

Many compensation schemes for multistage amplifiers have been investigated and reported [3–5, 7]. Techniques similar to those used in general feedback control systems have been adapted to use with electronic amplifiers. These methods include lead-magnet works, pole splitting, nested Miller compensation as well as signal level variable components. However, most compensation methods require more circuit area and more

complex design than the dominant pole approach used in the classic op-amp architecture. Special problems of integrated circuit amplifiers which include lack of large sized capacitors, parasitic coupling, and package parasitic and on/off chip load problems make the compensation more difficult than discrete component amplifiers.

The most widely used method of compensating integrated circuit op-amps is undoubtedly pole splitting in which the amplifier stage with the smallest bandwidth is further narrow-banded by a compensating capacitor that creates a well-defined dominant pole that sets both open and closed loop bandwidth of the overall amplifier.

This work is concerned with the compensation techniques for operational amplifiers and will explore new and novel methods of achieving compensation in feedback amplifiers that do not limit the bandwidth of closed loop performance to the same degree that commonly used methods do. Specific tools and methodologies will be developed to allow comparison of the new methods with standard methods of compensation.

## II. FREQUENCY COMPENSATION TECHNIQUES

In general, operational amplifiers are amplifiers with an open loop gain high enough to ensure the closed loop transfer characteristic with negative feedback is approximately independent of the op-amp gain. An adequately high gain is the key requirement of an op-amp to utilize the negative feedback configuration.

The single stage amplifier typically has good frequency response and could achieve a phase margin of 90° assuming the gain bandwidth is ten times higher than the single pole. However, the dc gain of the single amplifier is generally not high enough and is even less for submicron CMOS transistors. In general, op-amps require at least two gain stages. As a result, op-amp circuits have multiple poles. The poles contribute to the negative phase shift and may cause ∟FA to reach −180° before the unity gain frequency. The circuit will then oscillate due to the negative phase margin. It leads to the necessity of altering the amplifier circuit to increase the phase margin and stabilize the closed loop circuit. This process is called "compensation." By intuition, two different approaches may be taken to stabilize the circuit. The most straightforward way is to make the gain drop faster in order for the phase shift to be less than −180° at the unity gain frequency. This method achieves stability by reducing the bandwidth of the amplifier. The most popular pole splitting method uses this procedure. Another compensation method pushes the phase crossover frequency out by decreasing the total phase shift. In my case, the number of the poles of the op-amp needs to be minimized while still providing enough gain. Pushing the phase crossover frequency out is the basic idea of approaches like introducing zeros to cancel the poles or using feedforward paths to improve the phase margin without narrow-banding the bandwidth as much as the pole splitting method does.

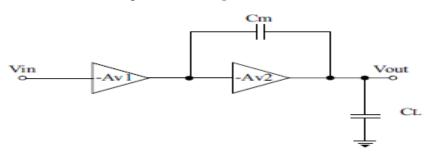

# Single Miller Compensation (SMC)

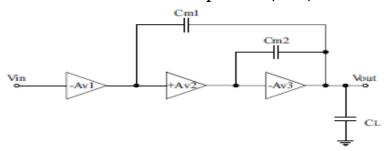

## Nested Miller Compensation (NMC)

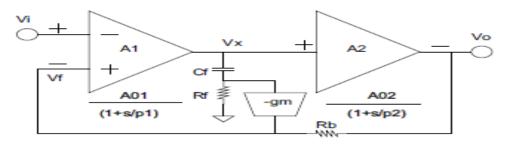

# Simplified model of the feedforward compensated operational amplifier

### III. DESIGN OF OP AMP

Many gain boosting schemes have been present to improve the gain of an op-amp. These gain enhancing methods often require complicated circuit structures and high supply voltage, and may produce a limited output voltage swing. Multiple stage amplifiers may be used for higher gain analog circuit designs. Many compensation schemes for multistage amplifiers have been investigated. However, most compensation methods require more circuit area and more complex design than the dominant pole approach used in the classic opamp architecture. Other high-gain CMOS op-amps have been investigated in previous work [8–14], but most did not achieve gains higher than 100 dB. A few achieved a gain ranging from 120 dB to 130 dB. These CMOS op-amp designs use up to five cascaded gain stages to achieve the high gain. The highest reported was the simulated 140 dB [10] unbuffered op amp with three cascaded gain stages. In general, high gain architectures need complex compensation to stabilize the op-amp and generally require more than one compensation capacitor.

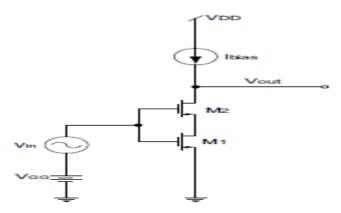

Composite Cascode Amplifier

## IV. METHODOLOGY AND TECHNIQUES

The design guide here is to apply the feed forward intuition on the system model and do the mathematical analysis to check if the idea works theoretically. After the feasibility is verified with theory, the feed forward scheme is then going to be evaluated by a system level simulation. Many different versions of SPICE simulators and MATLAB simulators already have built-in system level models of the circuit blocks. System level simulation can be done within a short time compared to the device level simulation. For accuracy and other practical issues, a mixed simulation method combining the system level simulation with the device level simulation is a very efficient and viable way to assess the creative design method.

#### V. CONCLUSIONS

Compensation methods of op amps are investigated along with their pros and cons in order for designers to have a guide to choose the approach suitable for different situations. This dissertation proposes a creative feedforward compensation method which overcomes the serious drawback of bandwidth narrowing by the widely used pole-splitting method. It can improve the phase margin as well as optimize the bandwidth of the op amp. The feedforward method can be easily applied to the existing popular two gain stage op amp architectures with very little alteration. The mathematical derivation and circuit simulation demonstrate the advanced properties and improved performance of this feedforward compensation technique.

This proposed innovative feedforward compensation method of op amps is explored by a creative mixed mode design methodology. This design approach combines intuition, mathematical analysis, and mixed level simulation. The mixed level simulation is comprised of both system level simulation and device level simulation for some critical analog circuit path. In this way, the behavior of new design ideas can be verified in an effective way as well as providing sufficient accuracy to predict the circuit performance realistically.

#### VI. REFERENCES

- [1]. Y. Taur, "Cmos design near the limit of scaling," IBM Journal of Research and Development, vol. 46, no. 2/3, pp. 213–222, March/May 2002.

- [2]. D. J. Comer and D. T. Comer, "Using the weak inversion region to optimize input stage design of CMOS op amps," Circuits and Systems II: Express Briefs, vol. 51, no. 1, pp. 8–14, Jan. 2004.

- [3]. P. Gray and R. Meyer, "Recent advances in monolithic operational amplifierdesign," IEEE Transactions on Circuits and Systems, vol. CAS-21, no. 3, pp.317–327, May 1974.

- [4]. D. Johns and K. Martin, Analog Integrated Circuit Design. New York: JohnWiley & Sons, Inc., 1996.

- [5]. J. Huijsing, R. Hogervorst, and K.-J. de Langen, "Low-power low-voltage vlsioperational amplifier cells," IEEE Transactions on Circuits and Systems, vol. 42,no. 11, pp. 841–852, Nov. 1995.

- [6]. P. E. Allen and D. R. Holberg, CMOS Analog Circuit Design, 2nd Ed. NewYork: Oxford University Press, 2002.

- [7]. W. Black, D. Allstot, and R. Reed, "A high performance low power CMOSchannel filter," IEEE J. Solid-State Circuits, vol. SC-15, no. 6, pp. 929–938,Dec. 1980.

- [8]. A. L. Coban and P. E. Allen, "A 1.75 v rail-to-rail CMOS op amp," Proc. OfIEEE International Symposium on Circuits and Systems, vol. 5, pp. 497–500, Jun. 1994.

- [9]. R. G. Eschauzier, R. Hogervorst, and J. H. Huijsing, "A programmable 1.5 vCMOS class-ab operational amplifier with hybrid nested miller compensation for 120 db gain and 6 mhzugf," IEEE J. Solid-State Circuits, vol. 29, no. 12,pp. 1497–1504, Dec. 1994.

- [10]. J. Purcell and H. S. Abdel-Aty-Zohdy, "Compact high gain CMOS op amp design using comparators," Proceedings of the 40th IEEE Midwest Symposium onCircuits and Systems, vol. 2, pp. 1050–1052, Aug. 1997.