International Conference on Advances in Materials, Computing and Communication Technologies In Association with International Journal of Scientific Research in Science and Technology Volume 9 | Issue 1 | Print ISSN: 2395-6011 | Online ISSN: 2395-602X (www.ijsrst.com)

# Low Power Design of MIPS RISC Processor

T. Latha, A. V. Varshitha, K. T. Vibisha, N. S. Saranya, Shiny Jose

Department of Electronics and Communication Engineering, St. Xavier's Catholic College of Engineering,

Chunkankadai, Nagercoil, Tamil Nadu, India

# ABSTRACT

The aim of the paper is to design a reversible control unit for 32 bit RISC processor using VHDL code. RISC or Reduced Instruction Set Computer is a design philosophy that has become a mainstream in scientific and engineering applications. Increasing performance and gate capacity of recent FPGA devices permits complex logic systems to be implemented on a single programmable device. Low power design of MIPS processor involves the use of reversible logic based design. The circuit of control unit is synthesized using Xilinx ISE. The parameters such as power and delay are estimated. The work is proceeded with the reversible logic based implementation.

Key words: MIPS, reversible logic, VHDL, control unit, datapath unit.

# I. INTRODUCTION

The need for low power design for control unit and data path design of a MIPS RISC processor is an increasing demand in many applications. By Moore's law, the number of transistors is doubled every 18 months. But the exponential increase in transistor count can increase the heat dissipation. Minimizing heat dissipation lead to development of reversible logics which can yield no information loss due to one to one mapping between input and output. The conventional logic gates are irreversible and have information loss, leading to heat dissipation.

Any Microprocessor and Microcontroller are designed by utilizing the two computing architectures, which are Complex Instruction Set Computing (CISC) and Reduced Instruction Set Computing architectures (RISC). The CISC processor architecture depends on Instruction Set architecture. The CISC processor utilizes the more number of operands and addressing modes in its instruction set. The RISC processor uses a less number of directions compared with the CISC processor. Comparing to CISC, RISC CPU have more advantages, such as faster speed, simplified structure, and easier implementation and so on. RISC CPU is extensive use in embedded system. The MIPS processor structure depends on the RISC processor. The processor utilizes the 5 pipeline stages, which are Instruction Fetch (IF), Instruction Decoder (ID), Execute (EX), Memory Access (MEM) and Write Back (WB). The MIPS single-cycle processor plays out all the pipeline stages in one clock cycle. This work involves the design of a reversible MIPS processor. The design includes a reversible control unit and a reversible data path unit.

**Copyright: O** the author(s), publisher and licensee Technoscience Academy. This is an open-access article distributed under the terms of the Creative Commons Attribution Non-Commercial License, which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited

### **II. LITERATURE REVIEW**

Galrani Tina, R.D [1] designed to performance Improvement of MIPS Architecture by Adding New Features. The main features of RISC processor are the instruction set can be improved to speed instruction execution. No microcode is needed for single cycle execution. All instructions are fixed bit in length. This simplifies the instruction fetch mechanism since the location of instruction boundaries is not a function of the instruction type. The RISC approach allows 32 bit processing power to be offered at much lower cost than was possible with a CISC, because of the smaller die size required to implement the processor.

T.Subhaahini, M.Kamaraju, K.Babulu [2] designed the single cycle Risc Micro Architecture Processor Using Clock Gating Technique. RISC based architectures are widely used to achieve low power. This work presents designing of single cycle RISC micro-architecture processor using clock gating technique. The single cycle processor performs the tasks of instruction fetch, instruction decode, execution, memory access and write-back all in one clock cycle. The RISC processor is designed for both single cycle and multi cycles by using the concept of MIPS. he main features of RISC processor are the instruction set can be improved to speed instruction execution. No microcode is needed for single cycle execution.

Preetam Bhole, Hari Krishna Moorthy[3] designed FPGA implementation of low power 32-bit RISC processor. The RISC 32 - bit processor architecture using Clock gating technique to perform the logical memory and branching the instruction. The different blocks are using to fetch, decode, execute, and memory read/write to execute four stage pipelining. The Harvard architecture used which contains memory space for data and program. To reduce the power of RISC core, clock gating technique is used in the architectural level as an effective low power method. Vishala A.Tyamanavar, Jayashr C.Nidagundi [4] designed FPGA implementation of a 32 – bit MIPS processor. The most important feature of the RISC processor is that this processor is very simple and support load/store architecture. The important components of this processor include the Arithmetic Logic Unit, Shifter, Rotator and Control unit. The RISC processor is designed for both single cycle and multi cycles by using the concept of MIPS.

Sarika U. Kadam, S.D. Mali [5] proposed a 16-bit RISC processor using a parallel programming language called VHDL. It is simulated and synthesized using Xilinx ISE 13.1i. Pipelining is used to make processor faster. In Pipelining instruction cycle is divided into parts so that more than one instruction can be operated in parallel. Number of instructions is designed for this processor. When the proposed work compared with previous processors, it can be seen that proposed processor has less delay.

ShilpaKodgire Pranjali S. Kelgaonkar, [6] implemented the design of 32 bit MIPS RISC Processor. The purpose of RISC microprocessor is to execute a minuscule batch of instructions, with the intention of proliferating the celerity of the processor. A Reduced Instruction Set compiler (RISC) is a microprocessor that had been designed to perform a small set of instructions, with the aim of increasing the overall speed of the processor. The RISC processor is designed based on MIPS instruction set. MIPSbased RISC architecture having operations like addition, subtraction, etc.

Mohit N. Topiwala, N. Saraswathi [7], proposed 32-bit MIPS based RISC processor is implemented successfully with pipeline functionalities. Every instruction is executed in one clock cycle with 5-stage pipelining. This design shows the implementation of MIPS based CPU capable of handling various R -type, J-type and I-type of instruction and each of these categories has a different format. These instructions are verified successfully through testbench. Designing Forwarding unit and hazard detection unit to overcome the data dependencies was critical task and

it was implemented successfully. The design is implemented using VerilogHDL and synthesized using Cadence RTL complier using typical libraries of TSMC 0.18 urn technology. Design of MIPS processor is optimized both in timing and area. Also complete ASIC flow till RTL to GDS II have done using Cadence SoC Encounter, and analyzed the complete physical design flow.

Mrs. Rupali S. Balpande and Mrs. Rashmi S. Keote [8] have designed FPGA based instruction Fetch and Decode Module of 32-bit (MIPS) processor. Through analysis of function and theory of RISC CPU instruction decoder module, they designed instruction decoder (ID) module of 32-bit CPU by pipelining.

Soumya Murthy and Usha Verma [9] proposed FPGA based 32 Bit RISC Core using DLX Architecture for power optimization. By using fetch, decode, ALU, comparator, GPR memory, execute, pipelined RISC processor core is developed using DLX architecture. Using low power technique, the processor is designed to reduce power consumption of the core.

V.N.Sireesha and D.Hari Hara santhosh [10]designed FPGA implementation of a MIPS risc processor. The RISC processors the instructions can be executed with the help of stages by using clock cycles. The instruction can be divided into four stages i.e. fetch, decode, execute and write back. The most important feature of the RISC processor is that this processor is very simple and support load/store architecture. The important components of this processor include the Arithmetic Logic Unit, Shifter, Rotator and control unit.The RISC processor is designed for both single cycle and multi cycles by using the concept of MIPS.

# **III. MIPS DESIGN**

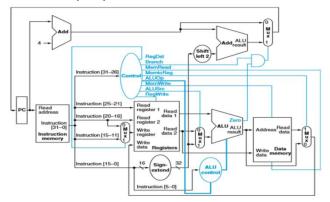

MIPS (Microprocessor without Interlocking Pipelining Stages) is a RISC processor that can execute an entire instruction in one cycle. The cycle time is limited by the slowest instructions. The RISC processor architecture consists of Arithmetic Logic Unit (ALU), Control Unit (CU), Barrel Shifter, Booth's Multiplier, Register File and Accumulator. RISC processor is designed with load/store architecture, meaning that all operations are performed on operands held in the processor registers and the main memory can only be accessed through the load and store instructions.

One shared memory for instructions (program) and data with one data bus and one address bus between processor and memory . Instruction and data are fetched in sequential order so that the latency incurred between the machine cycles can be reduced. For increasing the speed of operation RISC processor is designed with five stage pipelining. The pipelining stages are Instruction Fetch (IF), Instruction Decode (ID), Execution (EX), Data Memory (MEM), and Write Back (WB).

Fig.1 The simple datapath with the control unit

# IV. DESIGN OF CONTROL UNIT

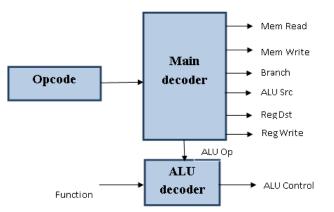

The control unit generates all the control signals needed to control the coordination among the entire component of the processor. This unit generates signals that control all the read and write operation of the register file, and the data memory. It is also responsible for generating signals that decide when to use the multiplier and when to use the ALU. Fig.2 shows the block diagram of the control circuit of MIPS processor.

Fig.2 Block diagram of a control unit of MIPS processor

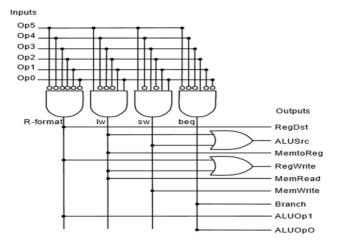

The setting of the control lines is completely determined by the opcode fields of the instruction. Table 1 shows the control signals generated for various groups of instructions such as arithmetic, load/store and branch instructions. Fig.3 shows the logic circuit for the main control unit.

Table 1 Generation of control signals for main control unit

| Instructi | R | Α  | Μ  | R  | Μ  | Μ   | Br | Α | Α |

|-----------|---|----|----|----|----|-----|----|---|---|

| on/       | е | L  | e  | е  | e  | e   | an | L | L |

| Opcode    | g | U  | m  | g  | m  | m   | ch | U | U |

|           | D | Sr | to | W  | R  | W   |    | 0 | 0 |

|           | s | с  | -  | r  | ea | rit |    | р | р |

|           | t |    | R  | it | d  | e   |    | 1 | 2 |

|           |   |    | eg | е  |    |     |    |   |   |

| R-format  | 1 | 0  | 0  | 1  | 0  | 0   | 0  | 1 | 0 |

| (000000)  |   |    |    |    |    |     |    |   |   |

| lw        | 0 | 1  | 1  | 1  | 1  | 0   | 0  | 0 | 0 |

| (100011)  |   |    |    |    |    |     |    |   |   |

| SW        | Х | 1  | Х  | 0  | 0  | 1   | 0  | 0 | 0 |

| (101011)  |   |    |    |    |    |     |    |   |   |

| beq       | Х | 0  | Х  | 0  | 0  | 0   | 1  | 0 | 1 |

| (000100)  |   |    |    |    |    |     |    |   |   |

Fig.3 Logic diagram of main control unit

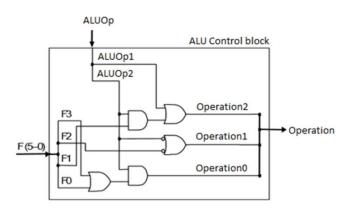

In order to design the logic for this ALU control unit, a truth table is developed. The input of the truth table is a 2-bit ALUOp and a 6-bit Function code, and the output is a 3-bit ALU control signals (Table 2). The logic circuit of the ALU control unit is shown in Fig.3.

Table 2 Generation of control signals for ALU controlunit

| ALUOp |     | Funct field |   |   |   |   |   | Operati |

|-------|-----|-------------|---|---|---|---|---|---------|

| ALUOp | ALU | F           | F | F | F | F | F | on      |

| 1     | Op0 | 5           | 4 | 3 | 2 | 1 | 0 |         |

| 0     | 0   | Х           | Х | Х | Х | Х | Х | 010     |

| Х     | 1   | Х           | Х | Х | Х | Х | Х | 110     |

| 1     | Х   | Х           | Х | 0 | 0 | 0 | 0 | 010     |

| 1     | Х   | Х           | Х | 0 | 0 | 1 | 0 | 110     |

| 1     | Х   | Х           | Х | 0 | 1 | 0 | 0 | 000     |

| 1     | Х   | Х           | Х | 0 | 1 | 0 | 1 | 001     |

| 1     | Х   | Х           | Х | 1 | 0 | 1 | 0 | 111     |

Fig.4 Logic circuit of ALU control unit

#### Low power reversible logic control unit

Power has become an important aspect in the design of general purpose processors. The RISC processor consume too much power compared with other processor. To minimize the power of control unit in RISC Core, reversible logic technique is used in the architectural level which is an efficient low power technique. Low power consumption helps to reduce the heat dissipation, lengthen battery life and increase device reliability. Low-power embedded processors are used in a wide variety of applications including cars, phones, digital cameras, printers, and other such devices. The reason for their wide use is that they are small; therefore, they do not take up much area and are cost effective to fabricate. There are various low power consumption technique such as clock gating, power gating, reversible logic gate etc. In this paper the design of control unit was done by using logic gate.

#### **Reversible logic gates**

A reversible gate realizes a reversible function, computation done by a gate is reversible in nature, that means for a gate g the gate g' implement inverse transformation.

Some of the basic gates are given below:

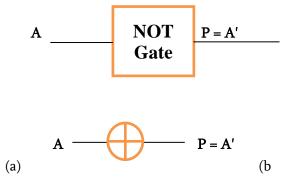

There are lot of reversible logic techniques. Here we use NOT and Toffoli reversible gates to reduces the power of control unit. A Not gate is a  $1\times1$  reversible gate is shown in Fig.5. The input is A and the output is P = A' which is reversible.

#### Table 3 Truth Table of NOT Gate

| Input | Output |

|-------|--------|

| Α     | Р      |

| 0     | 1      |

| 1     | 0      |

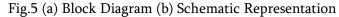

Toffoli gate:In 1982 Toffoli give a new gate called Toffoli gate. It is a  $3\times3$  gate and can be generalized up to  $n\times n$  size. As per definition target line flips when all control lines are set. In this design the Toffoli reversible gate is used .

Fig.6:3×3Toffoli gate (a)block diagram (b) schematic representation

Table 4 Truth table of Toffoli gate

| Input |   |   | Output |   |   |  |

|-------|---|---|--------|---|---|--|

| A     | В | С | Р      | Q | R |  |

| 0     | 0 | 0 | 0      | 0 | 0 |  |

| 0     | 0 | 1 | 0      | 0 | 1 |  |

| 0     | 1 | 0 | 0      | 1 | 0 |  |

| 0     | 1 | 1 | 0      | 1 | 1 |  |

| 1     | 0 | 0 | 1      | 0 | 0 |  |

| 1     | 0 | 1 | 1      | 0 | 1 |  |

| 1     | 1 | 0 | 1      | 1 | 1 |  |

| 1     | 1 | 1 | 1      | 1 | 0 |  |

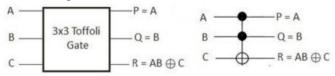

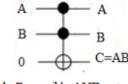

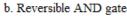

By mapping Gate the irreversible logic gates in these main control unit and ALU control unit into reversible logic gates, the power can be minimized. This includes the conversion of conventional irreversible AND, OR gates into a reversible AND, OR gates.

a. Conventional AND gate

Fig.7 AND gate representations

## Fig.8 OR gate representations

In Fig.7, third input C is put as '0' in the Toffoli gate to convert it into an AND gate. Similarly, in Fig.8, third input is '1' to obtain the Toffoli gate as an OR gate. These can be included in the design of reversible control unit.

### V. SIMULATION RESULT

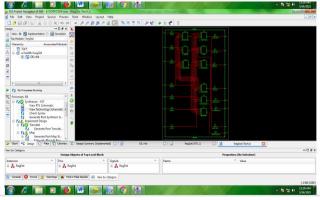

The simulation results for reversible control unit based MIPS RISC processor for various control bits are shown as in Fig.9. Fig.10 and Fig.11 shows the RTC schematic and Technology schematic with reversible control unit. Table 5 shows the device utilization summary, delay and power for MIPS RISC processor with and without reversible logic.

Fig.10 RTL schematic

| Ngn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | × 16                           | 3 3828                  | 212    | -  | 100<br>25/2             | 254  |                    |   |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------|--------|----|-------------------------|------|--------------------|---|-----|

| Ro Module: AngOot<br>Hierarchy Associated Medule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                             |                         |        | ÷  | -U                      | -    |                    |   |     |

| 10FF 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.01 10 10                     |                         | ö      | Q  | Ö                       | Q    | j.                 |   |     |

| - 9 (S) 06.144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                              |                         | Ö      | Ģ  |                         | Ċ,   |                    |   |     |

| () An Processes Survey                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                              |                         | 24     | 13 | Ö                       | 5    | -                  |   |     |

| Processes DE<br>Processes DE<br>View RTL Schematic<br>View Tschnology Schematic<br>Check Synta<br>Generate Proch Synthesis Su-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000                           |                         |        |    | No. of Concession, Name | 0    | 0                  |   |     |

| Organisation (Construction) Organisation Organistation Organisation Organisation Organisation Or | *                              |                         |        |    | Q                       | Q.   |                    |   |     |

| Start Pd Desgr O Has O Libraria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e 🔳 Design Summary (Dr         | piervertud) 🔲 🔒         | DE.ind |    | 0.0                     | RegD | 8 (97U)            | 0 | -08 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ign Objects of Top Level Block |                         |        |    |                         |      | Properties: (No Se |   |     |

| starces * Pins<br>▲ RegDat = ♣                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RegDat                         | Signate<br>III 👗 RegDat | * Na   |    |                         |      | * Yelu             |   |     |

| Console O trons 1 Vierman &                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ped in Pass Results III Vice 5 | r Category              |        |    |                         |      |                    |   |     |

Fig.11 Technology schematic

| Table   | 5   | Comparison    | of   | delay,  | power | and | device |

|---------|-----|---------------|------|---------|-------|-----|--------|

| utiliza | tio | n of MIPS RIS | SC p | rocesso | r     |     |        |

| Utilization report | MIPS RISC  | MIPS RISC  |  |  |

|--------------------|------------|------------|--|--|

|                    | Processor  | Processor  |  |  |

|                    | without    | With       |  |  |

|                    | reversible | reversible |  |  |

|                    | logic      | logic      |  |  |

| Delay(ns)          | 0.905      | 1.99       |  |  |

| Number of slice    | 15         | 9          |  |  |

| LUTs               |            |            |  |  |

| Number of bonded   | 85         | 15         |  |  |

| IOBs               |            |            |  |  |

| Power(W)           | 0.084      | 0.042      |  |  |

#### VI. CONCLUSION

The use of VHDL for modeling is especially appealing since it provides a formal description of the system and allows the use of specific description styles to cover the different abstraction levels (architectural, register transfer and logic level). The reversible MIPS RISC Processor is proposed because of its area, less complexity, less power as well as faster speed. In particular, the MIPS RISC processor uses reduced instruction set hence results to minimize human effort and reversible logic for low power designs.

### VII. REFERENCES

- [1]. Galani Tina, R.D.Daruwala, 'Performance Improvement of MIPS Architecture by Adding New Features", International Journal of Advanced Research in Computer Science and Software Engineering, Volume 3, Issue 2, February 2013, ISSN: 2277 128X.

- [2]. T.Subhashini, M.Kamaraju, K.Babulu, "Single Cycle Risc Micro Architecture Processor Using Clock Gating Technique" International Journal of Scientific & Technology Research Volume 8, ISSUE 12, December 2019 ISSN 2277-8616.

- [3]. Preetam Bhosle, Hari Krishna Moorthy. FPGA implementation of low power pipelined 32-Bit RISC processor,International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-1 Issue-3, August 2012.

- [4]. Vishala A.Tyamanavar, Jayashree C. Nidagundi. FPGA Implementation of a 32-Bit MIPS Processor International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 NCRACES – 2019 Conference Proceedings.

- [5]. Sarika U. Kadam, S. D. Mali, "Design of RISC processor using VHDL", International Journal of Research Granthaalaya, Vol.4 (Iss.6): June, 2016, DOI:10.5281/zenodo.56647.

- [6]. Pranjali S. Kelgaonkar, Prof. ShilpaKodgire, "Design of 32 Bit MIPS RISC Processor Based on Soc", International Journal of Latest Trends in Engineering and Technology (IJLTET), January 2016.

- [7]. Mohit N. Topiwala, N. Saraswathi, "Implementation of a 32-bit MIPS based RISC processor using cadence," 2014 IEEE International Conference Advanced on Communication Control and Computing Technologies (ICACCCT), ISBN No. 978-1-4799-3914-5/14/©2014 1EEE.

- [8]. Rupali S. Balpande, Rashmi S. Keote, "Design of FPGA based instruction fetch and decode

Module of 32-bit (MIPS) processor," International Conference on communication Systems and Network Technologies, DOI:10.1109/CSNT.2011.91,2011.

- [9]. Soumya Murthy, Usha Verma, "FPGA based Implementation of power optimization of 32 bit RISC core using DLX Architecture," 2015 International Conference on Computing Communication Control and Automation, DOI 10.1109/ICCUBEA.2015.191.

- [10]. V.N.Sireesha and D.Hari Hara Santosh, "FPGA Implementation of a MIPS RISC Processor", International journal of computer technology and applications, volume 3, issue 3, pp. 1251 – 1253, issn: 2229 – 6093